## L584

PRELIMINARY DATA

### MULTIFUNCTION INJECTION INTERFACE

- DRIVES ONE OR TWO EXTERNAL DAR-LINGTONS

- DUAL AND SINGLE LEVEL CURRENT CONTROL

- SWITCHMODE CURRENT REGULATION

- ADJUSTABLE HIGH LEVEL CURRENT DURA-TION

- WIDE SUPPLY RANGE (4.75 46V)

- TTL-COMPATIBLE LOGIC INPUTS

- THERMAL PROTECTION

- DUMP PROTECTION

#### DESCRIPTION

The L584 is designed to drive injector solenoids in electronic fuel injection systems and generally inductive loads for automotive applications. The device is controlled by two logic inputs and features switchmode regulation of the load current driving an external darlington and an auxiliary one for the current recirculation. A key feature of the L584 is flexibility. It can be used with a variety of darlingtons to match the requirements of the load and it allows both simple and two level current control. Moreover,

# DIP16 (12 + 2 + 2) ORDERING NUMBER : L584

the drive waveshape can be adjusted by external components. Other features of the device include dump protection, thermal shutdown, a supply voltage range of 4.75 - 46V and TTL-compatible inputs. The L584 is supplied in a 16 lead Powerdip package which uses the four center pins to conduct heat to the PC board copper.

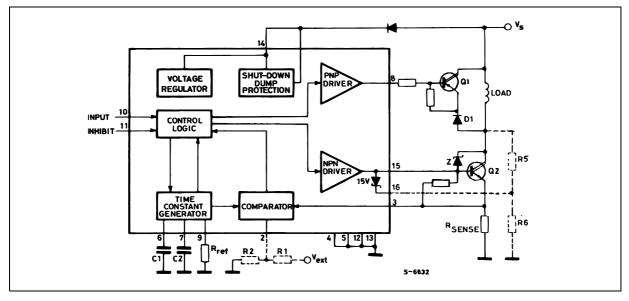

#### **BLOCK DIAGRAM**

November 1988

1/13

#### **PIN CONNECTION**

| DUMP                                        |         | INTERNAL             |

|---------------------------------------------|---------|----------------------|

| PROTECTION<br>HOLDING<br>CURRENT<br>CONTROL | (2 15   |                      |

| SENSING                                     | 3 14    | SUPPLY<br>VOLTAGE    |

| GND                                         | 4 13    | GND                  |

| GND                                         | 5 12    | GND                  |

| PEAK<br>CURRENT<br>TIMER                    | 6 11    |                      |

| TIME<br>CONSTANT                            | 7 10    | INPUT                |

| PNP<br>OUTPUT                               | 8 9     | REFERENCE<br>VOLTAGE |

|                                             | 5- 6831 | 1                    |

#### ABSOLUTE MAXIMUM RATINGS

| Symbol            | Parameter                                                                                                                                                                                                  | Value                            |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|

| Vs                | DC Supply Voltage (pin 1 open)<br>Positive Transient Voltage<br>(pin 1 connected to V <sub>S</sub> , $\pi_f$ fall time constant = 100ms)<br>(5ms $\leq t_{rise} \leq 10ms$ , $R_{source} \geq 0.5\Omega$ ) | – 0.2V min; +50V Max<br>+60V Max |  |  |

| V <sub>1</sub>    | Input Voltage (pins 10, 11)                                                                                                                                                                                | – 0.2V min; +7V Max              |  |  |

| Vr                | External Reference Voltage (pin 2)                                                                                                                                                                         | – 0.2V min; +7V Max              |  |  |

| V <sub>sens</sub> | Sense Voltage (pin 3)                                                                                                                                                                                      | – 0.2V min; +7V Max              |  |  |

| V <sub>8</sub>    | Max D.C. and Transient Voltage                                                                                                                                                                             | 50V                              |  |  |

| l <sub>r</sub>    | Reference Current (pin 9)                                                                                                                                                                                  | 5mA Max                          |  |  |

| Tstg, Tj          | Storage and Junction Temperature Range                                                                                                                                                                     | –55 to 150°C                     |  |  |

#### THERMAL DATA

| Symbol                 | Parameter                           | Value | Unit |      |

|------------------------|-------------------------------------|-------|------|------|

| R <sub>th j-pins</sub> | Thermal Resistance Junction-pins    | Max.  | 15   | °C/W |

| R <sub>th j-amb</sub>  | Thermal Resistance Junction-ambient | Max.  | 80   | °C/W |

$^{\ast}$  Obtained with the GND pins soldered to printed circuit with minimized copper area.

#### **PIN FUNCTIONS**

| N°     | Name                    | Functions                                                                                                                                                                                                      |  |  |  |

|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1      | Dump Protection         | With pin 1 connected to pin 14 the device is protected against dump voltage $\leq 60$ .<br>The protectio.n operates at V <sub>S</sub> $\geq$ 32V (typ.). If this protection is not used the pin m be left open |  |  |  |

| 2      | Holding Current Control | The voltage V <sub>set</sub> applied to this pin sets the holding current level.                                                                                                                               |  |  |  |

| 3      | Sensing                 | Connection for load current sense resistor. Vazlue sets the peak and holding current levels. $I_P = 0.45/R_S$ (typ.); $I_h = V_{set}/R_s$ . (see block diagram and fig. 4).                                    |  |  |  |

| 4      | Ground                  | Ground Connection. With pins 5, 12 and 13 conducts heat to pc board copper.                                                                                                                                    |  |  |  |

| 5      | Ground                  | See pin 4.                                                                                                                                                                                                     |  |  |  |

| 6      | Peak Current Timer      | A capacitor connected between this pin and ground sets the duration of the high level current ( $t_2$ in fig. 4)                                                                                               |  |  |  |

| 7      | Discharge Time Constant | A capacitor connected between this pin and ground sets the duration of $t_{off}$ (fig. 4 grounded, the current switchmode control is suppressed.                                                               |  |  |  |

| 8      | PNP Driving Output      | Current sink for external PNP darlington (for recirculation). $I_{dp} = 35$ Ir (typ).                                                                                                                          |  |  |  |

| 9      | Reference Voltage       | A resistor connected between this pin and ground sets the internal current reference, $I_r$ . The recommended value is $1.2k\Omega$ giving $Ir = 1mA$ (typ.).                                                  |  |  |  |

| 10     | Input                   | TTL-compatible Input. A high level on this pin activates the output, driving the load.                                                                                                                         |  |  |  |

| 11     | Inhibit                 | TTL-compatible Inhibit Input. A high level on this input disables the output stages and logic circutry, irrespective of the state of pin 10.                                                                   |  |  |  |

| 12, 13 | Ground                  | See Pin 4.                                                                                                                                                                                                     |  |  |  |

| 14     | Supply Voltage          | Supply Voltage Input.                                                                                                                                                                                          |  |  |  |

| 15     | NPN Driving Output      | Current Source for External NPN Darlington (load driver).Idn = 100 Ir (typ.)                                                                                                                                   |  |  |  |

| 16     | Internal Clamping       | Internal Clamp Zener for Fast Turn-off.                                                                                                                                                                        |  |  |  |

000

| Symbol            | Parameter                                     | Test Condiction                                                 | Min.                                                 | Тур. | Max.                    | Unit     |

|-------------------|-----------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------|------|-------------------------|----------|

| Vs                | Operating Supply Voltage                      | Pin 1 Open                                                      | 4.75                                                 |      | 44                      | V        |

| Vd                | Dump Protection Threshold                     | $Pin 1 = V_S$                                                   | 28                                                   |      | 36                      | V        |

| Rd                | Dump Protection Input Resistance              | Pin 1 to GND                                                    | 18                                                   |      | 50                      | kΩ       |

| lq                | Quiescent Current                             | Pin 14                                                          |                                                      |      | 45                      | mA       |

| Vi                | Input Threshold Voltages                      | Pin 10, 11<br>Low<br>High                                       | 2.0                                                  |      | 0.8                     | > >      |

| li                | Input Current                                 | Pin 10, 11<br>Low<br>High                                       | -100                                                 |      | -250                    | μΑ<br>μΑ |

| Vr                | Reference Voltage                             | Pin 9                                                           | 1.15                                                 |      | 1.35                    | V        |

| R <sub>r</sub>    | Reference Resistor Range                      | Pin 9 to GND<br>I <sub>r</sub> = V <sub>r</sub> /R <sub>r</sub> | 1                                                    |      | 3.3                     | kΩ       |

| l <sub>6</sub>    | Peak Duration Control Current                 | Pin 6<br>V <sub>pin 6</sub> ≤ 1.8V                              | I <sub>r</sub> /9.50   I <sub>r</sub> /6.00          |      | l <sub>r</sub> /6.00    | А        |

| V <sub>6th</sub>  | Peak Duration Control<br>Comparator Threshold | Pin 6                                                           | 1.20                                                 |      | 1.6                     | V        |

| V <sub>6SAT</sub> | Pin 6 Saturation Voltage                      | Pin 6<br>(discharge state)                                      |                                                      |      | 200                     | mV       |

| I <sub>7</sub>    | Off Duration Control Current                  | Pin 7<br>$V_{pin 7} \leq 1.8V$                                  | (I <sub>r min</sub> )/9.50   (I <sub>r max</sub> )/6 |      | <sub>r max</sub> )/6.00 | A        |

| V <sub>7th</sub>  | Off Duration Control<br>Comparator Threshold  | Pin 7                                                           | 1.20                                                 |      | 1.6                     | V        |

| V <sub>7SAT</sub> | Pin 7 Saturation Voltage                      | Pin 7<br>(discharge state)                                      |                                                      |      | 200                     | mV       |

| V <sub>spt</sub>  | Peak Current Threshold Voltage                | Pin 3                                                           | 400                                                  |      | 500                     | mV       |

| Vset              | Holding Current Set Voltage Range             | Pin 2                                                           | 0                                                    |      | 2                       | V        |

| V <sub>set</sub>  | Holding Current Set Voltage Range             | Pin 3, Peak Value, dV/dt $\leq$ 1V/s                            | V <sub>set</sub> –<br>0.01                           |      | V <sub>set</sub> + 0.01 | V        |

| l3                | Pin 3 Bias Current                            | V <sub>pin 3</sub> = 600mV                                      | -200                                                 |      |                         | μA       |

| V <sub>cl</sub>   | Recirculation Zener Clamping<br>Voltage       | Pin 16 to Pin 15 @ 200mA into Pin 16                            | 13.5                                                 |      | 18.5                    | V        |

| I <sub>dn</sub>   | NPN Driver Source Current                     | V <sub>pin 15</sub> = 0V                                        | 70 x I <sub>r</sub>   140 x I <sub>r</sub>           |      | А                       |          |

| I <sub>dp</sub>   | PNP Driver Sink Current                       | Vpin 8 ≥ 4.75V                                                  | 25 x l <sub>r</sub>   60 x l <sub>r</sub>            |      | 00                      | А        |

**ELECTRICAL CHARACTERISTICS** (Vs (Pin 14) = 14.4V;  $-40 \le Tj \le 105^{\circ}C$ ;  $R_{ref} = 1.20K\Omega$  unless otherwise specified; refer to fig. 1)

4/13

#### **APPLICATION INFORMATION**

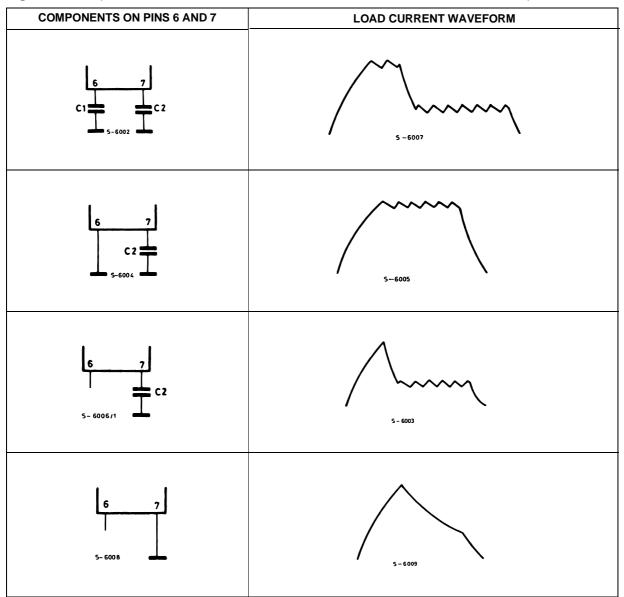

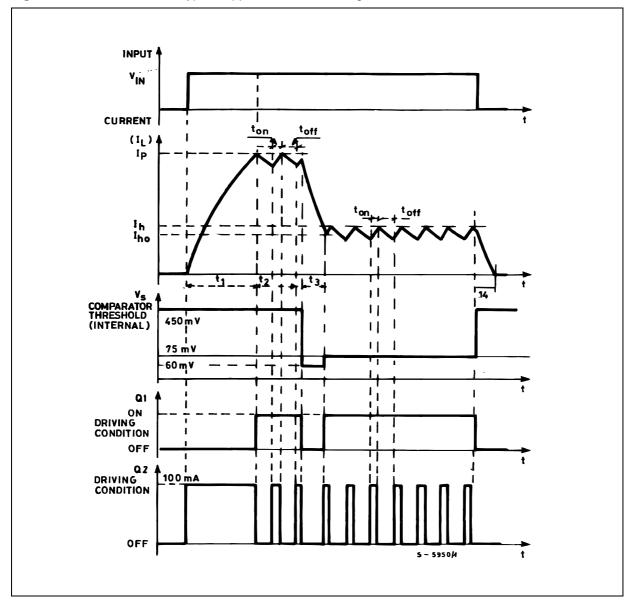

Controlled by a logic input and an inhibit input (both TTL compatible), the device drives the external darlington(s) to produce a load current waveform as shown in figure 4. This basic waveform shows that the device produces an initial high level current in order to ensure a fast opening, followed by a holding level current as long as the input is active. Both the peak and holding current are regulated by the L584's switchmode circuitry. The duration of the high level current and the values of the peak and the holding currents can be adjusted by external components.

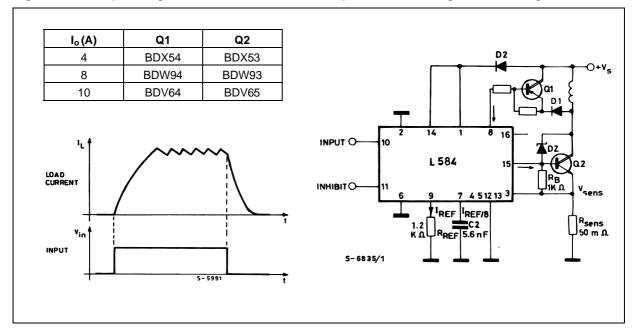

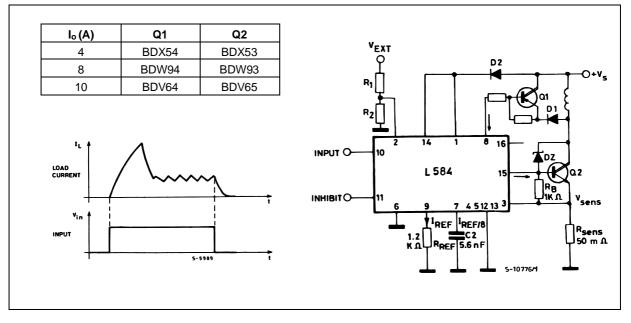

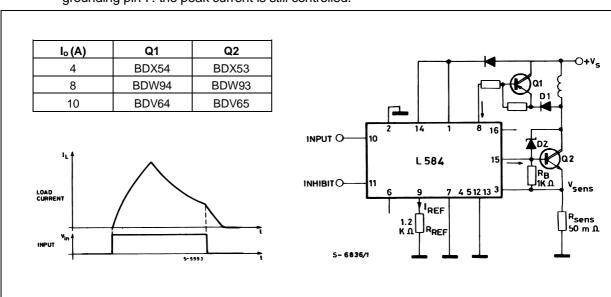

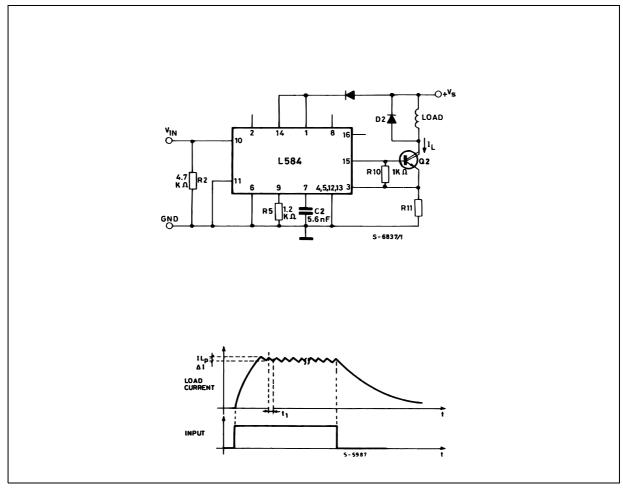

Moreover, by omitting C1, C2 or both it is possible to realize single-level current control, a transitory peak followed by a regulated holding current or a simple peak (figure 1).

The peak and holding current values are always re-

Figure 1 : Components Connected to Pins 6 and 7 Determine the Load Current Waveshape.

ferred, in the following formula, to  $I_E$ , emitter current of the external darlington Q2,

$$I_E = I_{LOAD} + I_{dn}$$

because the sensing detection is on the darlington emitter (not directly on the load).

The peak current level  $I_{\text{p}},$  is set by the sensing resistor,  $R_{\text{s}},$  and is found from :

$$_{\rm p} = 0.45 / R_{\rm s} (typ)$$

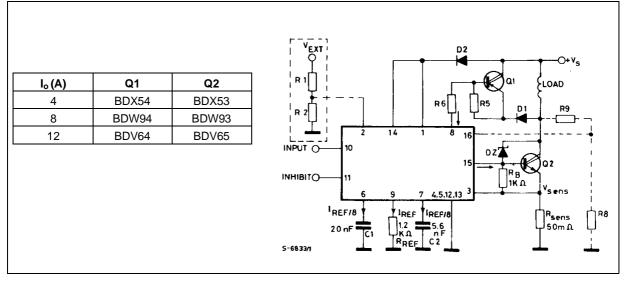

The peak value of holding current level,  $I_h$ , is set by a voltage (V<sub>set</sub>) applied to pin 2, giving :

$$I_{hp} = V_{setth} / R_s = (V_{set} \pm 10 mV)/R_s$$

The peak to hold current ratio is fixed by  $V_{set}$ :

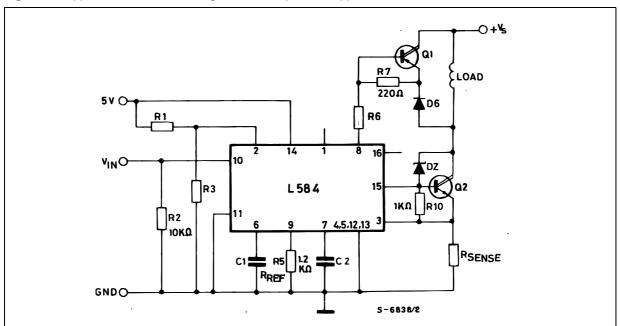

$V_{set}$  is fixed by an external reference and a voltage divider ( $V_{ext}$ , R1, R2 in fig 2) :  $V_{set} = V_{ext} * R2 / (R1 + R2)$

Due to the particular darlington storage time and the device reaction time not very significant differences can be found between  $I_p$  and  $I_h$  values based on the previous formula and the real values seen in the applications.

If the holding current function is not used, pin 2 cannot be left floating and it must be connected to GND.

Figure 2 : Application Circuit Showing the Optional Components. In particular it illustrates how the holding current level is adjusted independently of the peak current (with R1, R2, V<sub>ext</sub>) and how the internal zener clamp is connected. This circuit produces the waveforms shown in Fig. 4.

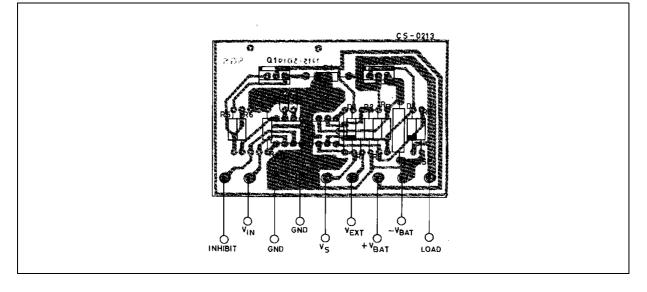

Figure 3 : P.C. Board and Components Layout of the Circuit of Fig. 2 (1 : 1 scale).

SGS-THOMSON

6/13

The drive current for the two darlingtons and the waveform time constants are all defined in turn by a resistor between pin 9 and ground.

The recommended value for I<sub>r</sub> is 1mA which is obtained with a 1.2K $\Omega$  resistor. The darlington drive currents are given by :

$PNP : I_{dp} = 35 I_r typ.$  NPN :  $I_{dn} = 100 I_r typ.$

The duration of the high current level ( $t_2$  in fig 4) is set by a capacitor connected between pin 6 and

ground. This capacitor, C1 is related to the duration,  $t_2,\,by$  :

$$t_2 = C_1 \frac{V_{6th} - V_{6sat}}{I_6} = 12 \frac{C_1}{I_{ref}} (typ.)$$

The discharge time constant ( $t_{off}$  in fig 4) is set by a capacitor  $C_2$  between pin 7 and ground and is found from :

$$t_{off} = C2 \cdot \frac{V_{7th} - V_{7sat}}{I_7} = 12 \frac{C_r}{I_{ref}} (typ)$$

Figure 4 : Waveforms of the Typical Application Circuit of Fig. 2.

Figure 5 : When pin 6 is grounded, as shown here, the injector current is regulated at a single level.

Figure 6 : In this application circuit, pin 6 is left open to give a single peak followed by a regulated holding current.

Figure 7 : Switchmode control of the current can be suppressed entirely by leaving pin 6 open and grounding pin 7. the peak current is still controlled.

Figure 8 : Applications circuit using only one darlington with a single level of the injector current.

To have a very short off time when the L584 input goes LOW, an internal zener is available on pin 16. This zener is used with an external divider, R8, R9, as shown in figure 2. Suitable values can be found from :

$$V_{\text{pin 16}} \cong 15V + V_{\text{BEQ2}} + V_{\text{Rsense}}$$

$$V_{\text{CQ2}} \cong V_{\text{pin 16}} \cdot \frac{\text{R9} + \text{R8}}{\text{R8}}$$

( $V_{CQ2}$  is the voltage at the collector of Q2.  $V_{CQ2}$  max is 47V if the pin 8 is used for slow recirculation as in fig. 2).

To ensure stability, a small capacitor (about 200pF) must be connected between the base and collector of Q2 when pin 16 is used.

A different opportunity for a fast off time is based on the use of the external zener diode Dz. In this case also the maximum Dz voltage value is 47V.

#### LOAD DUMP PROTECTION

To protect the device against the positive load dump it is necessary to connect pin 1 to V<sub>S</sub>. In this case, if V<sub>S</sub> is higher than 32V, the device turns off Q<sub>2</sub> and turns on Q<sub>1</sub>. The external resistor R<sub>6</sub> must be used (see application circuit) to avoid that pin 8 voltage exceeds 50V during load dump. R<sub>6</sub> must be :

$$R_6 > \frac{V_{DUMP} - V_8}{I_{dp}}$$

where  $V_{DUMP}$  is the dump voltage value and  $V_8$  : 4.75V <  $V_8$  < 47V.

For this  $R_6$  value, the minimum supply voltage  $V_{Smin}$  guaranteeing Q1 operation is given by :

$$V_{Smin} = R6 \left( \frac{lp}{B_{Q1}} (+2) \frac{V_{BEQ1}}{R_5} \right) + V_{8sat}$$

In relation to  $V_{Smin}$  it is no more verified  $I_{dp} = 35 I_{ref}$  (typ) even if the system correct operation is completely guaranteed.

The L584 application circuit suggested in these notes allows the use of inductive loads with the lowest possible series resistance (compatible with constructional requirements) and therefore reduces notably the power dissipation.

For example, an electronic injector driven from 14.4V which draws 2.4A has a series resistance of  $6\Omega$  and dissipates 34.56W. Using this circuit a injector with a  $1\Omega$  series resistance can be used and the power dissipation is :

$P_{d} = R_{L}I_{L}^{2} + V_{D}I_{L} (1 - \sigma) + V_{sat} \cdot IL \sigma + R_{s} I_{L}^{2} \sigma$

where  $R_L$  = resistance of injector = 1 $\Omega$

$$V_D = drop \ across \ diode, \ V_D \cong 1V$$

$V_{sat}$  = saturation voltage of Q2,  $\cong 1V$

$$R_S = R11 = 185m\Omega$$

$$\sigma = duty cycle = 20\%$$

therefore :

$Pd \cong 5.76 + 1.92 + 0.48 + 0.21 = 8.37W$

This given two advantages : the size (and cost) of the injector is reduced and the drive current is reduced from 2.4A to about 0.4A.

The application circuit of figure 9 is very similar to figure 2 except that it shows the use of two supplies : one for the control circuit, one for the power stage.

Figure 9 : Application circuit showing how two separate supplies can be used.

In this application it is assumed that the 5V supply for L584 is taken from a logic supply, which is already protected, against load dump transients and vol-tage reversal.

Pin 1 must be left open, as shown in fig. 9, if  $V_{S}$  is always lower than 46V even during the voltage transients.

Note that  $t_{\text{off}}$  is also related to the required current ripple  $\Delta I$  on the peak or on the holding current level by :

$$t_{off} = - \ln \frac{(I_o - \Delta I) R_L + V_{off}}{I_o R_L + V_{off}}$$

Where : lo is the initial current value in OFF condition (equal to Ip or IH in accordance to the current level considered),

$$VOFF = VDIODE + VCEQ1$$

$\mathsf{R}_\mathsf{L}$  is the series resistance value of the inductance  $\mathsf{L}$  :

Therefore C<sub>2</sub> can be dimensioned directly by :

$$C_2 = \frac{I_{REF} L}{12} - \frac{I_{R}}{R_L} - \frac{(I_0 - \Delta I) R_L + V_{OFF}}{I_0 R_L + V_{OFF}}$$

Note that  $t_{\text{off}}$  is the same for both the peak and holding current.

ton time is given by :

$$t_{on} = \frac{L}{R} \ln \frac{V_{on} - R(I1 - \Delta I)}{V_{on} - RI1}$$

where : I1 is the final current value in ON condition (equal to  $I_p$  or  $I_H$  in accordance to the current level considered),

$$R = R_L + R_{SENSE}$$

$$V_{on} = V_S - V_{CE}satQ2$$

If the constant times are respectively

$$\frac{L}{R}$$

> 20 toff and  $\frac{L}{R}$  > 20 ton

it is possible to consider a purely inductive load and therefore :

$$t_{off} = L \frac{\Delta I}{V_o}$$

;  $t_{on} = L \frac{\Delta I}{V_{on}}$

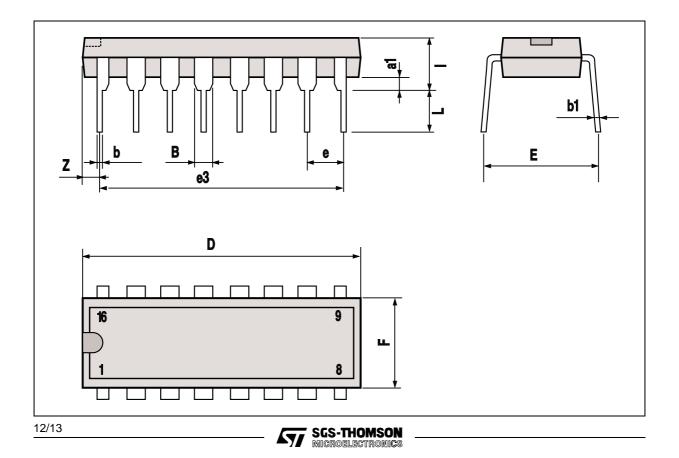

#### **DIP16 PACKAGE MECHANICAL DATA**

| DIM. | mm   |       |      | inch  |       |       |  |

|------|------|-------|------|-------|-------|-------|--|

|      | MIN. | TYP.  | MAX. | MIN.  | TYP.  | MAX.  |  |

| a1   | 0.51 |       |      | 0.020 |       |       |  |

| В    | 0.77 |       | 1.65 | 0.030 |       | 0.065 |  |

| b    |      | 0.5   |      |       | 0.020 |       |  |

| b1   |      | 0.25  |      |       | 0.010 |       |  |

| D    |      |       | 20   |       |       | 0.787 |  |

| E    |      | 8.5   |      |       | 0.335 |       |  |

| е    |      | 2.54  |      |       | 0.100 |       |  |

| e3   |      | 17.78 |      |       | 0.700 |       |  |

| F    |      |       | 7.1  |       |       | 0.280 |  |

| I    |      |       | 5.1  |       |       | 0.201 |  |

| L    |      | 3.3   |      |       | 0.130 |       |  |

| Z    |      |       | 1.27 |       |       | 0.050 |  |

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1994 SGS-THOMSON Microelectronics - All Rights Reserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands - Singapore -Spain - Sweden - Switzerland - Taiwan - Thaliand - United Kingdom - U.S.A.